# 3V-40V Vin, 150mA, 2.5uA IQ, Low-Dropout Regulator

### **FEATURES**

Wide Input Range: 3V-40V

With up to 45V Transient Input Voltage

Maximum Output Current: 150mA

Output Voltage:

3.3V and 5V (Fixed Output)

Other Output Voltage Options (Need contact SCT sales)

Output Voltage Accuracy:

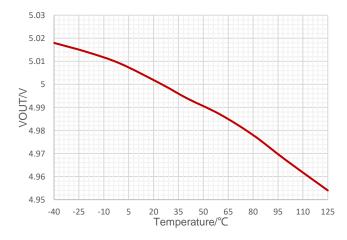

➤ T<sub>J</sub>= 25°C : ±1%

► T<sub>J</sub>= -40°C ~ 125°C : ±2%

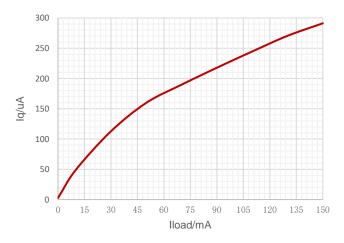

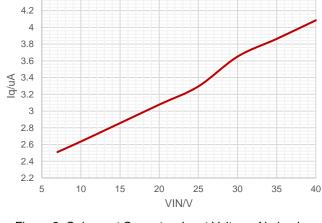

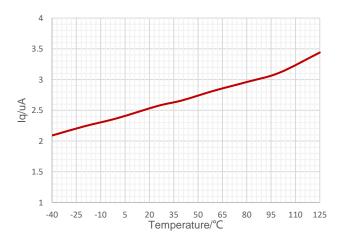

Low Quiescent Current: 2.5uA

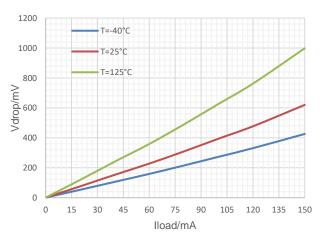

Low Dropout Voltage :

204mV at 50mA load current

643mV at 150mA load current

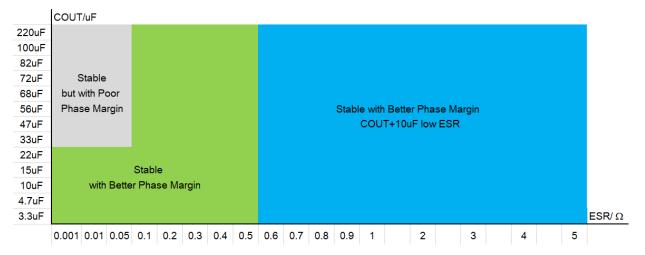

Support Output Capacitors Range:

> 3.3uF~220uF

$\triangleright$  Low-ESR:  $0.001\Omega \sim 5 \Omega$

660us Internal Soft-start Time

Integrated Short-Circuit Protection with OCFB (Over Current Fold-back) Feature

Over-Temperature Protection

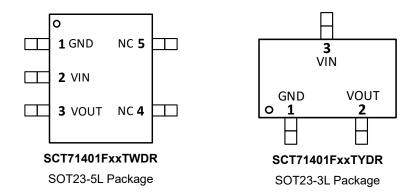

Available Package: SOT23-5L / SOT23-3L

### **APPLICATIONS**

- Handheld Devices with Battery Power Supply

- POS and Power Tools

- Meters and Smoke Detector

- Industrial Control

### **DESCRIPTION**

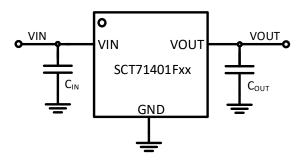

The SCT71401 series products is a low-dropout linear regulator designed to operate with a wide input-voltage range from 3 V to 40 V (45V transient input voltage) and 150mA output current. The SCT71401 series products is stable with 3.3uF~220uF output capacitors, and 10uF ceramic capacitor is recommended.

Only 2.5-µA typical quiescent current at light load makes the SCT71401 series products ideal choices for portable devices with battery power supply and an optional solution for powering microcontrollers (MCUs) and CAN/LIN transceivers in always-on systems.

The SCT71401 series products integrated short-circuit and overcurrent protection with OCFB (Over Current Fold-back) feature, which makes the device more reliable during transient high-load current faults or shorting events.

The SCT71401 series products provide fixed 3.3V and 5V output voltage versions, and also could provide 1.2V, 1.8V, 2.5V, 3V, 4.2V and 4.5V fixed output voltage versions, please contact SCT sales if needed.

The SCT71401 series products is available in SOT23-5L and SOT23-3L packages, for other package options, please contact SCT sales.

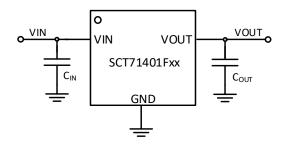

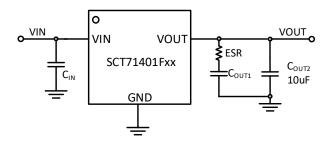

#### TYPICAL APPLICATION

For more information <a href="www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

### **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Revision 1.0: Release to production.

Revision 1.1: Update the thermal information and the thermal characteristic.

Revision 1.2: Update the thermal information and the thermal characteristic.

Revision 1.3: Update the TAPE AND REEL INFORMATION.

Revision 1.4: Update DEVICE ORDER INFORMATION and TAPE AND REEL INFORMATION.

Revision 1.5: Remove one package type.

### **DEVICE ORDER INFORMATION**

| Orderable Device | Output<br>Voltage | Package  | Package<br>Marking | PINS | MSL | Transport Media,<br>Quantity |

|------------------|-------------------|----------|--------------------|------|-----|------------------------------|

| SCT71401F50TWDR  | Fixed 5.0V        | SOT23-5L | 1F50               | 5    | 3   | Tape & Reel, 3000            |

| SCT71401F33TWDR  | Fixed 3.3V        | SOT23-5L | 1F33               | 5    | 3   | Tape & Reel, 3000            |

| SCT71401F50TYDR  | Fixed 5.0V        | SOT23-3L | 1F50               | 3    | 3   | Tape & Reel, 3000            |

| SCT71401F33TYDR  | Fixed 3.3V        | SOT23-3L | 1F33               | 3    | 3   | Tape & Reel, 3000            |

2 For more information <u>www.silicontent.com</u> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

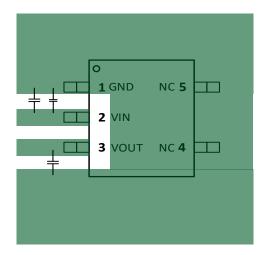

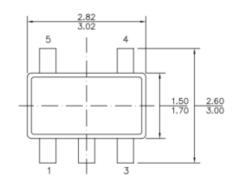

### **PIN CONFIGURATION**

### **PIN FUNCTIONS**

# **SOT23-5L/SCT71401Fxx:**

| PIN NUMBER | NAME | PIN FUNCTION                 |

|------------|------|------------------------------|

| 1          | GND  | Ground reference pin.        |

| 2          | VIN  | Input voltage pin            |

| 3          | VOUT | Regulated output voltage pin |

| 4          | NC   | No connection                |

| 5          | NC   | No connection                |

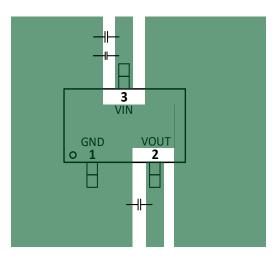

# SOT23-3L/SCT71401Fxx:

| PIN NUMBER | NAME | PIN FUNCTION                 |

|------------|------|------------------------------|

| 1          | GND  | Ground reference pin.        |

| 2          | VOUT | Regulated output voltage pin |

| 3          | VIN  | Input voltage pin            |

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER      | DEFINITION                        | MIN   | MAX | UNIT |

|----------------|-----------------------------------|-------|-----|------|

| Vin            | Input voltage range               | 3     | 40  | V    |

| Vout           | Output voltage range              | 1.2   | 5   | V    |

| Cin            | Input capacitor                   | 2.2   |     | uF   |

| Соит           | Output capacitor                  | 3.3   | 220 | uF   |

| ESR            | Output capacitor ESR requirements | 0.001 | 5   | Ω    |

| TA             | Operating ambient temperature     | -40   | 125 | °C   |

| T <sub>J</sub> | Operating junction temperature    | -40   | 125 | °C   |

### ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature range unless otherwise noted (1)

| PARAMETER                      | DEFINITION                   | MIN  | MAX | UNIT |

|--------------------------------|------------------------------|------|-----|------|

| V <sub>IN</sub> <sup>(1)</sup> | Maximum input voltage range  | -0.3 | 45  | V    |

| Vout                           | Maximum output voltage range | -0.3 | 5.5 | V    |

| T <sub>J</sub> <sup>(2)</sup>  | Junction temperature range   | -40  | 150 | °C   |

| $T_{stg}$                      | Storage temperature range    | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

### **ESD RATINGS**

| PARAMETER | DEFINITION                                                                                   | MIN | MAX | UNIT |

|-----------|----------------------------------------------------------------------------------------------|-----|-----|------|

| Vesd      | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>     | -7  | +7  | kV   |

|           | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -1  | +1  | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 150°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

### THERMAL INFORMATION

The value of Reja and Rejc given in this table is only valid for comparison with other packages and cannot be used for design purposes. Because they were simulated in accordance with JESD 51-7. They do not represent the performance obtained in an actual application. For design information see Power Dissipation and Thermal Performance section.

The value of R<sub>0JA\_EVM</sub> is the tested results based on our EVM, and is more useful for thermal design. Even if it still do not represent the thermal performance of customer's PCB design, but it was a good starting point for thermal performance design.

The PCB information of our EVM: 2-layer, 1oz Cu, 50mm x 30mm size.

The values given in this table are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB), thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the device. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual values of the below table.

| Package Type | R <sub>0JA</sub> <sup>(1)</sup> | R <sub>0JC</sub> <sup>(2)</sup> | R <sub>0JA_EVM</sub> (3) | UNIT   |  |

|--------------|---------------------------------|---------------------------------|--------------------------|--------|--|

| SOT23-5L     | 213.45                          | 167.56                          | 103.81                   | °C/\\/ |  |

| SOT23-3L     | 252.03                          | 170.99                          | 112.18                   | °C/W   |  |

- (1)  $R_{\theta JA}$  is junction to ambient thermal resistance, based on JESD51-7.

- (2)  $R_{\theta JC}$  is junction to case thermal resistance, based on JESD51-7.

- (3)  $R_{\text{\tiny OJA EVM}}$  is junction to ambient thermal resistance, which is tested on SCT EVM.

For more information www.silicontent.com © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

### **ELECTRICAL CHARACTERISTICS**

V<sub>IN</sub>=V<sub>OUT</sub>+1V, C<sub>OUT</sub>=10uF, T<sub>J</sub>= -40°C~125°C, typical value is tested under 25°C.

| SYMBOL                  | PARAMETER                                   | TEST CONDITION                                                                     | MIN | TYP  | MAX | UNIT |  |

|-------------------------|---------------------------------------------|------------------------------------------------------------------------------------|-----|------|-----|------|--|

| Power Supply            |                                             |                                                                                    |     |      |     |      |  |

| Vin                     | Operating input voltage                     |                                                                                    | 3   |      | 40  | V    |  |

| \/                      | V <sub>IN</sub> UVLO Threshold              | V <sub>IN</sub> rising                                                             | 2.3 | 2.64 | 2.9 | V    |  |

| V <sub>UVLO</sub>       | Hysteresis                                  |                                                                                    |     | 210  |     | mV   |  |

| la .                    | Quiescent current from GND pin              | No load, V <sub>IN</sub> =V <sub>OUT</sub> +1V                                     |     | 2.5  |     | μA   |  |

| lq                      | Quiescent current from GND pin              | No load, V <sub>IN</sub> =12V                                                      |     | 2.6  |     | μA   |  |

| Regulated               | Output Voltage and Current                  |                                                                                    |     |      |     |      |  |

| 1/                      | 0.44                                        | T <sub>J</sub> = 25°C                                                              | -1% |      | 1%  |      |  |

| Vout                    | Output voltage accuracy                     | T <sub>J</sub> = -40°C~125°C                                                       | -2% |      | 2%  |      |  |

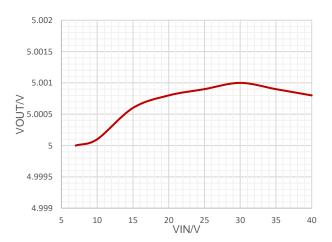

| ΔVоυт                   | Line regulation                             | V <sub>IN</sub> =V <sub>OUT</sub> +1V to 40V, or V <sub>IN</sub> >3V,<br>lout=10mA |     | 4.5  | 10  | mV   |  |

|                         | Load regulation                             | lout=1mA to 150mA                                                                  |     | 5    | 20  | mV   |  |

|                         | Dropout voltage <sup>(1)</sup>              | V <sub>IN</sub> =V <sub>OUT</sub> -0.1V ,lout =50mA                                |     | 204  |     | mV   |  |

| $V_{DROP}$              |                                             | V <sub>IN</sub> =V <sub>OUT</sub> -0.1V ,lout =100mA                               |     | 416  |     | mV   |  |

|                         |                                             | V <sub>IN</sub> =V <sub>OUT</sub> -0.1V ,lout =150mA                               |     | 643  |     | mV   |  |

| Гоит                    | Output current                              | V <sub>оит</sub> in regulation                                                     | 0   |      | 150 | mA   |  |

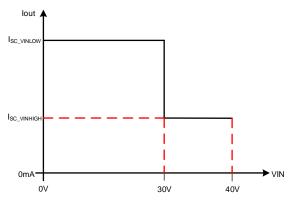

| Isc_vinLow              | Short current limit                         | V <sub>OUT</sub> =0V, VIN<30V                                                      |     | 300  |     | mA   |  |

| I <sub>SC_VINHIGH</sub> | Short current limit                         | V <sub>OUT</sub> =0V, VIN>30V                                                      |     | 100  |     | mA   |  |

|                         |                                             | I <sub>OUT</sub> =10mA, f=1kHz, C <sub>OUT</sub> =10μF                             |     | 63   |     | dB   |  |

| PSRR                    | Power supply rejection ratio <sup>(2)</sup> | Ιουτ=10mA, f=10kHz, Cουτ=10μF                                                      |     | 43   |     | dB   |  |

|                         |                                             | Ιουτ=10mA, f=100kHz, Cουτ=10μF                                                     |     | 52   |     | dB   |  |

| Soft-startu             | p                                           |                                                                                    |     |      |     |      |  |

| T <sub>SS</sub>         | Soft-start time                             |                                                                                    |     | 660  |     | us   |  |

| Thermal Pr              | rotection                                   |                                                                                    |     | -    |     | ·    |  |

| T <sub>SD</sub>         | Thermal shutdown threshold <sup>(3)</sup>   | T <sub>J</sub> rising                                                              |     | 170  |     | °C   |  |

| ופו                     |                                             | Hysteresis                                                                         |     | 20   |     | °C   |  |

<sup>(1)</sup> The dropout voltage is defined as  $V_{IN}$ - $V_{OUT}$ , when force  $V_{IN}$  is 100mV below the value of  $V_{OUT}$  for  $V_{IN}$ = $V_{OUT}$ (nom)+1V.

<sup>(2)</sup> PSRR is derived from bench characterization, not production test.

<sup>(3)</sup> Thermal shutdown threshold is derived from bench characterization, not production test.

### TYPICAL CHARACTERISTICS

Figure 1. Quiescent Current vs Output Current

4.4

Figure 2. Quiescent Current vs Input Voltage, No load

Figure 3. Quiescent Current vs Ambient Temperature

Figure 4. Dropout Voltage vs Output Current

Figure 5. Output Voltage vs Ambient Temperature at VOUT=5V

Figure 6. Output Voltage vs Input Voltage

# **TYPICAL CHARACTERISTICS (continued)**

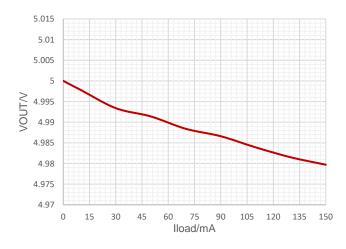

Figure 7. Output Voltage vs Output Current at VOUT=5V

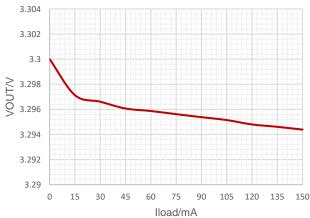

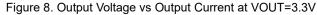

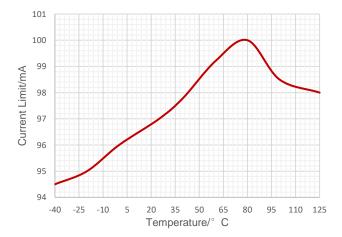

Figure 9. Output Current Limit vs Ambient Temperature at VIN<30V

Figure 10. Output Current Limit vs Ambient Temperature at VIN≥30V

# **TYPICAL CHARACTERISTICS (continued)**

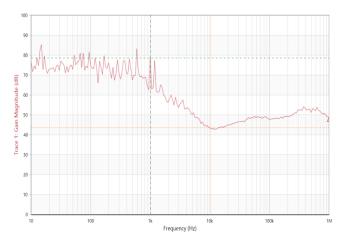

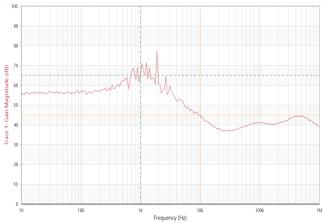

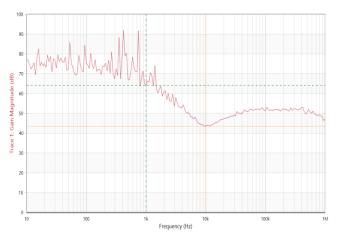

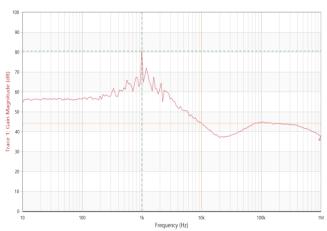

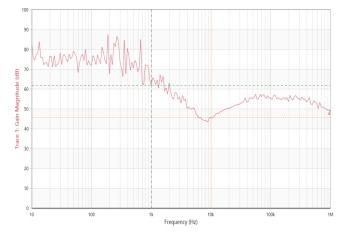

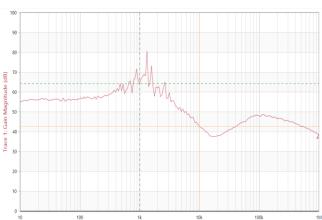

Figure 11. PSRR vs Frequency at lout=10mA, Cout=4.7uF

Figure 12. PSRR vs Frequency at lout=100mA, Cout=4.7uF

Figure 13. PSRR vs Frequency at lout=10mA, Cout=10uF

Figure 14. PSRR vs Frequency at lout=100mA, Cout=10uF

Figure 15. PSRR vs Frequency at lout=10mA, Cout=22uF

Figure 16. PSRR vs Frequency at lout=100mA, Cout=22uF

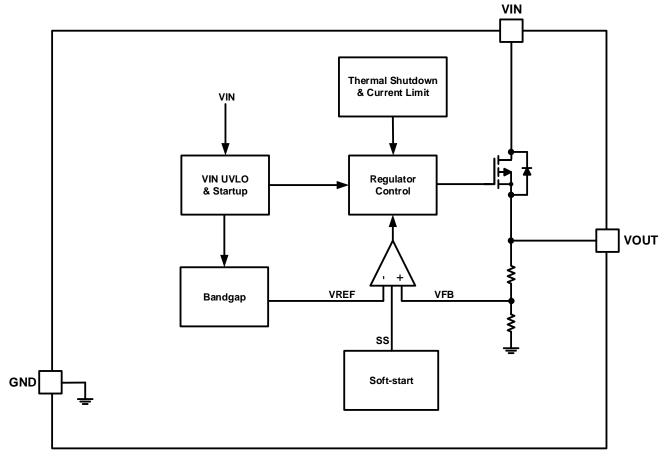

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 17. Functional Block Diagram

### **OPERATION**

#### Overview

The SCT71401 series products are 150mA wide input voltage range linear regulators with very low quiescent current. These voltage regulators operate from 3V to 40V DC input voltage with supporting 45V transient input voltage and consume 2.5µA quiescent current at no load.

The SCT71401 series products is stable with 3.3uF~220uF output capacitors, and 10uF ceramic capacitor is recommended. An internal 660us soft-start time avoids large inrush current and output voltage overshoot during startup.

The SCT71401 series products also provide the VIN input under-voltage lockout, over current protection, output hard short protection and thermal shutdown protection.

The SCT71401 series products are available in fixed voltage versions of 3.3V and 5V with 1% output voltage accuracy at room temp and 2% output voltage accuracy over operating conditions. The series products are available in SOT23-5L and SOT23-3L packages.

### **Regulated Output Voltage**

The SCT71401 series are available in fixed voltage versions of 3.3V and 5V. When the input voltage is higher than  $V_{\text{OUT(NOM)}} + V_{\text{DROP}}$ , output pin is the regulated output based on the selected voltage version. When the input voltage falls below  $V_{\text{OUT(NOM)}} + V_{\text{DROP}}$ , output pin tracks the input voltage minus the dropout voltage based on the load current. When the input voltage drops below UVLO threshold, the output keeps shut off.

The SCT71401 series products also could provide other fixed output voltage versions of 1.2V, 1.8V, 2.5V, 3V, 4.2V and 4.5V and other package options. Please feel free to contact SCT sales, if you need a new output voltage version or a new package option.

#### **Over Current Limit and Foldback Current Limit**

The SCT71401 series products has an internal current limit circuit that protects the regulator during transient high-load current faults or shorting events. The current limit is 300mA when VIN<30V, but SCT71401 supplies a fold-back current limit 100mA when VIN>30V.

The output voltage is not regulated when the device is in current limit. When a current limit event occurs, the regulator begins to heat up because of the increase in power dissipation. If thermal shutdown is triggered, the device turns off. After the device cools down, the internal thermal shutdown circuit turns the device back on. If the output current fault condition persists, the device cycles between current limit and thermal shutdown.

With the over current foldback limit feature, the SCT71401 series products would be more robust and safer when over current faults and shorting events occur. But it also requires the maximum loading current should be smaller than Isc during startup. The characteristic is shown in the following figure.

Figure 18. Current Limit with Foldback Feature

#### **Internal Soft-Start**

The SCT71401 series products integrates an internal soft-start circuit that ramps the reference voltage from zero volts to 0.6V reference voltage in 660us. The soft-start will reset during shutdown due to thermal overloading.

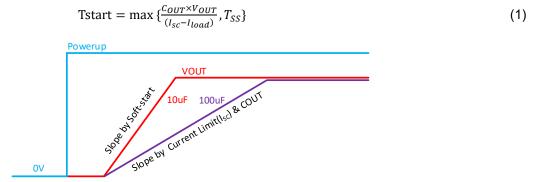

Below figure shows the startup waveform at small output capacitor and large output capacitor. When output capacitor is small, for example 10uF, the slope of VOUT is limited by soft-start. When output capacitor is large, for example 100uF, the slope of VOUT is limited by current limit (I<sub>SC VINLOW</sub>) at VIN<30V, and the slope of VOUT is limited by current limit (Isc VINHIGH), when VIN> 30V.

In SCT71401 series products, typical Tss is 660us, and typical Isc\_vinLow is 300mA and typical Isc\_vinHigh is 100mA, could use the following formula for initial startup time calculation.

Figure 19. Soft-start Waveform vs Output Capacitor

#### **Thermal Shutdown**

This device incorporates a thermal shutdown (T<sub>SD</sub>) circuit as a protection from overheating. For continuous normal operation, the junction temperature should not exceed the T<sub>SD</sub> trip point. The junction temperature exceeding the T<sub>SD</sub> trip point causes the output to turn off. When the junction temperature falls below the T<sub>SD</sub> trip point minus thermal shutdown hysteresis, the output turns on again.

### APPLICATION INFORMATION

### **Typical application 1:**

Figure 20. SCT71401 Typical Application Schematic

**Design Parameters**

| Design Parameters                        | Example Value                |

|------------------------------------------|------------------------------|

| Input Voltage                            | 12V Normal, 5.5V~40V         |

| Output Voltage                           | 5V or 3.3V                   |

| Maximum Output Current                   | 150mA                        |

| Output Capacitor Range (Cout)            | 3.3uF~22uF , recommends 10uF |

| Input Capacitor Range (C <sub>IN</sub> ) | >2.2uF , recommends 10uF     |

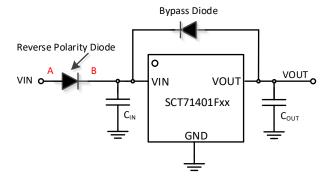

# **Typical application 2:**

Figure 21. SCT71401 Typical Application Schematic with Reverse Polarity Diode

**Design Parameters**

| Design Parameters                        | Example Value                |

|------------------------------------------|------------------------------|

| Input Voltage                            | 12V Normal, 5.5V~40V         |

| Output Voltage                           | 5V or 3.3V                   |

| Maximum Output Current                   | 150mA                        |

| Output Capacitor Range (Cout)            | 3.3uF~22uF , recommends 10uF |

| Input Capacitor Range (C <sub>IN</sub> ) | >2.2uF , recommends 10uF     |

In some applications, the VIN and the VOUT potential might be reversed, possibly resulting in circuit internal damage or damage to the elements. For example, the accumulated charge in the output pin capacitor flowing backward from the VOUT to the VIN when the VIN shorts to the GND. In order to minimize the damage in such case, use a capacitor with a capacitance less than 220µF. Also by inserting a reverse polarity diode in series to the VIN, it can prevent reverse current from reverse battery connection or the case, when the point A is short-circuited GND. If there may be any possible case point B is short-circuited to GND, we also recommend using a bypass diode between the VIN and the VOUT.

### Typical application 3:

Figure 22. SCT71401 Typical Application Schematic with Large Output Capacitor

Design Parameters

| Design Parameters                           | Example Value                |

|---------------------------------------------|------------------------------|

| Input Voltage                               | 12V Normal, 5.5V~40V         |

| Output Voltage                              | 5V or 3.3V                   |

| Maximum Output Current                      | 150mA                        |

| Output Capacitor Range (Cout1 and ESR)      | 3.3uF~220uF with ESR=0.5Ω~5Ω |

| Output Capacitor Range (C <sub>OUT2</sub> ) | recommends 10uF with low ESR |

| Input Capacitor Range (C <sub>IN</sub> )    | >2.2uF , recommends 10uF     |

For more information <a href="https://www.silicontent.com">www.silicontent.com</a> © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

#### **Input Capacitor and Output Capacitor**

SCT recommends adding a  $2.2\mu F$  or greater capacitor with a  $0.1\mu F$  bypass capacitor in parallel at VIN pin to keep the input voltage stable. Aluminum electrolytic capacitor or other capacitor with high capacitance is suggested for the system power with large voltage spike. The voltage rating of the capacitors must be greater than the maximum input voltage.

To ensure loop stability, the SCT71401 series products requires an output capacitor with a minimum effective capacitance value of  $3.3\mu F$ . And the series products could support output capacitor range from  $3.3\mu F$  to  $220\mu F$  and with an ESR range between  $0.001\Omega$  and  $5\Omega$ . SCT recommends selecting a X5R- or X7R-type  $4.7\mu F$ ~10 $\mu F$ 0 ceramic capacitor with low ESR over temperature range to improve the load transient response.

When using large output capacitor with higher ESR resistor, for example 100 $\mu$ F output electrolytic capacitor with 10 ESR resistor in the application, SCT recommends adding extra 10 $\mu$ F low ESR output capacitor parallel connection with the large electrolytic capacitor, this will eliminate the undershoot/overshoot voltage caused by the large ESR resistor and get better load transient performance.

Figure 23. SCT71401 Stability vs Output Capacitor

For more information www.silicontent.com © 2023 Silicon Content Technology Co., Ltd. All Rights Reserved

#### **Power Dissipation and Thermal Performance**

Power dissipation caused by voltage drop across the LDO and by the output current flowing through the device needs to be dissipated out from the chip. The maximum junction temperature is dependent on power dissipation, package, the PCB layout, number of used Cu layers, Cu layers thickness and the ambient temperature.

During normal operation, LDO junction temperature should not exceed 150°C, or else it may result in deterioration of the properties of the chip. Using below equations to calculate the power dissipation and estimate the junction temperature.

The power dissipation can be calculated using Equation 2. Because I<sub>GND</sub> « I<sub>OUT</sub>, the term V<sub>IN</sub> x I<sub>GND</sub> in Equation 2 could be ignored.

$$P_D = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{GND}$$

(2)

The junction temperature can be estimated using Equation 3. R<sub>BJA\_EVM</sub> is the junction-to-ambient thermal resistance based on customer's PCB. Verify the application and allow sufficient margins in the thermal design by the following method is used to calculate the junction temperature T<sub>J</sub>.

$$T_J = T_A + P_D \times R_{\theta JA\_EVM} \tag{3}$$

Reja\_evm is a critical parameter and depends on many factors such as the following:

- · Power dissipation

- · Air temperature/flow

- PCB area

- Copper heat-sink area

- · Number of thermal vias under the package

- Adjacent component placement

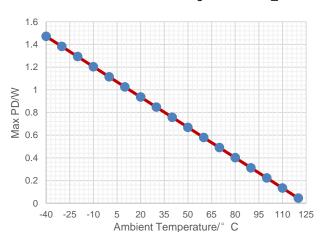

For the SCT71401 series products, the maximum allowable power dissipation of different packages was listed in the following table, and the test results are based on our EVM board, larger power dissipation will trigger thermal shutdown protection. As a result, we could calculate the R<sub>θJA\_EVM</sub> of different packages. The following table is just for your reference based on our EVM test, please leave enough margin when you design thermal performance.

The PCB information of our EVM: 2-layer, 1oz Cu, 50mm x 30mm size.

#### Thermal Performance of Different Packages Based on EVM Test

| Package  | Max Allowable PD (W)<br>(Not Trigger TSD,VOUT=5V) | Max Allowable PD (W)<br>(TJ≤125℃) | R <sub>0JA_EVM</sub> (°C/W) |

|----------|---------------------------------------------------|-----------------------------------|-----------------------------|

| SOT23-5L | 1.397                                             | 0.963                             | 103.81                      |

| SOT23-3L | 1.293                                             | 0.891                             | 112.18                      |

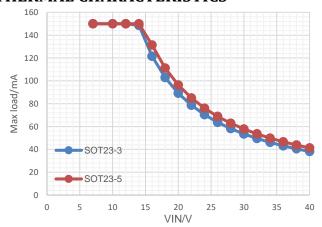

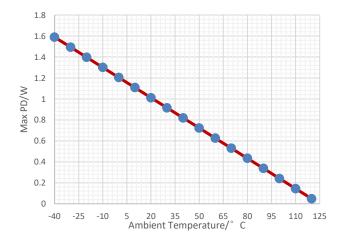

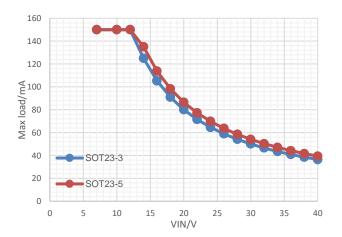

### THERMAL CHARACTERISTICS

Figure 24. Maximum Output Current vs Input Voltage, VOUT=5V of Different Packages ,TJ ≤ TSD\_R

Figure 26. Maximum Allowed Power Dissipation vs Ambient Temperature, SOT23-3L,TJ ≤ 125°C

Figure 28. Maximum Allowed Power Dissipation vs Ambient Temperature, SOT23-5L, $T_J \le 125^{\circ}C$

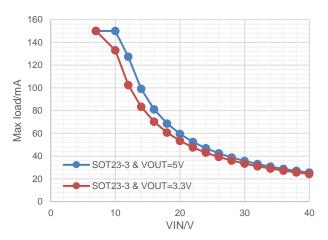

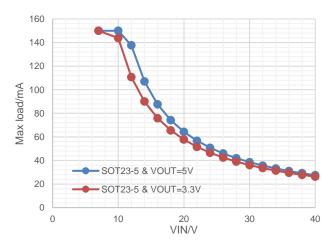

Figure 25. Maximum Output Current vs Input Voltage, VOUT=3.3V of Different Packages ,TJ ≤ TSD\_R

Figure 27. Maximum Output Current vs Input Voltage, SOT23-3L,TJ ≤ 125°C

Figure 29. Maximum Output Current vs Input Voltage,  $SOT23\text{-}5L, T_{J} \leq 125^{\circ}C$

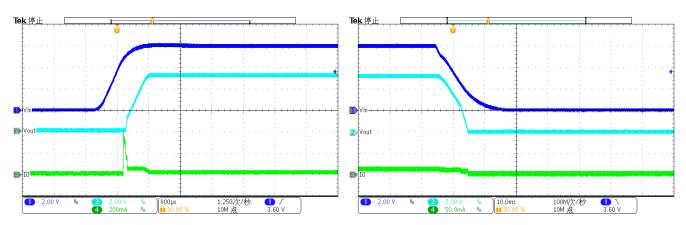

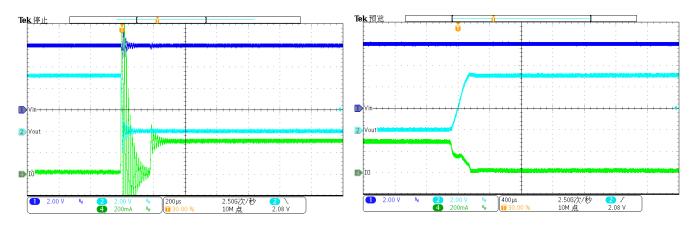

### **Application Waveforms**

Vin=Vout +1V, unless otherwise noted

Figure 32. Power up (Iload=10mA)

Figure 33. Power down (Iload=10mA)

Figure 34. Slow Power up (Iload=10mA)

Figure 35. Slow Power down (Iload=10mA)

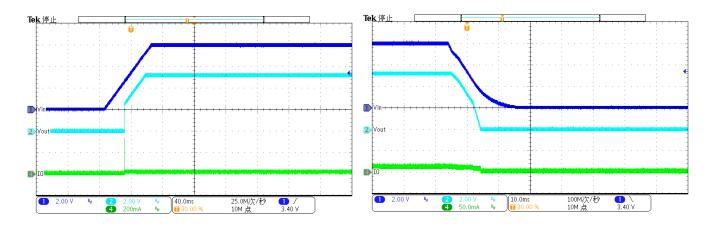

Figure 36. DC-DC Load Transient (40mA-110mA), VOUT=5V

Figure 37. DC-DC Load Transient (20mA-130mA),Vout=5V

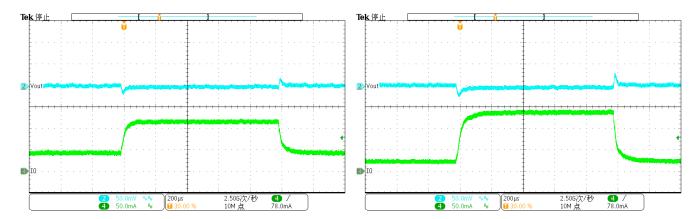

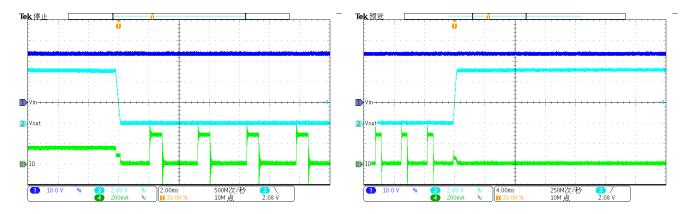

### **Application Waveforms(Continued)**

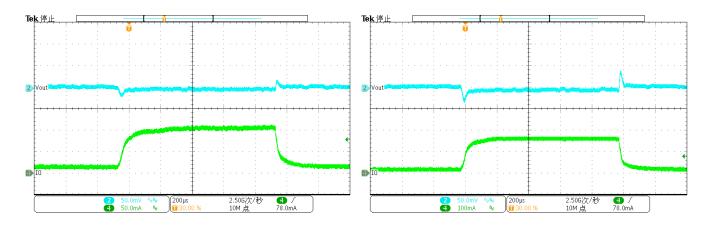

Vin=Vout +1V, unless otherwise noted

Figure 38. DC-DC Load Transient

(10mA-100mA),VOUT=5V

Figure 39. DC-DC Load Transient (10mA-150mA),VouT=5V

Figure 40. Enter Short Circuit Protection

Figure 41. Exit Short Circuit Protection

Figure 42. Enter Over Temperature Protection

Figure 43. Exit Over Temperature Protection

#### **Layout Guideline**

Proper PCB layout is a critical for SCT71401's stability, transient performance and good regulation characteristics. For better results, follow these guidelines as below:

- 1. Both input capacitors and output capacitors must be placed as close to the device pins as possible.

- 2. It is recommended to bypass the input pin to ground with a  $0.1\mu\text{F}$  bypass capacitor. The loop area formed by the bypass capacitor connection,  $V_{\text{IN}}$  pin and the GND pin of the system must be as small as possible.

- 3. It is recommended to use wide trace lengths or thick copper weight to minimize I×R drop and heat dissipation.

- 4. To improve the thermal performance of the device, and maximize the current output at high ambient temperature, SCT recommends spreading the copper under the thermal pad as far as possible and placing enough thermal vias on the copper under the thermal pad.

- 5. If using large electrolytic capacitor with high ESR resistor, SCT recommends adding a 10uF low ESR capacitor parallel connection with the large electrolytic capacitor.

Figure 44. PCB Layout Example

SCT71401FxxTWDR

Figure 45. PCB Layout Example

SCT71401FxxTYDR

### PACKAGE INFORMATION

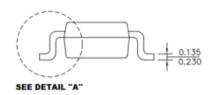

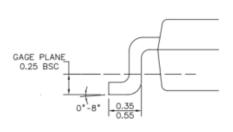

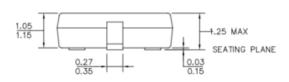

#### **TOP VIEW**

**FRONT VIEW**

SIDE VIEW

**DETAIL A**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE

- MOLD FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WIDTH DOES NOT INCLUDE

- INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS

- AFTER FORMING) SHALL BE 0.10

- MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-193,

- VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

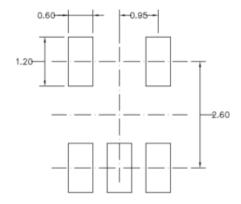

SOT23-5L Package Outline Dimensions

#### NOTE:

- 1. Drawing proposed to be made a JEDEC package outline MO-193 variation.

- 2. Drawing not to scale.

- 3. All linear dimensions are in millimeters.

- 4. Thermal pad shall be soldered on the board.

- 5. Dimensions of exposed pad on bottom of package do not include mold flash.

- 6. Contact PCB board fabrication for minimum solder mask web tolerances between the pins.

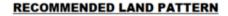

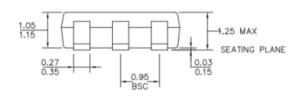

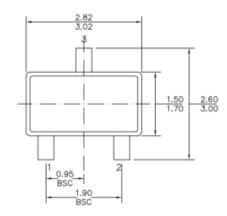

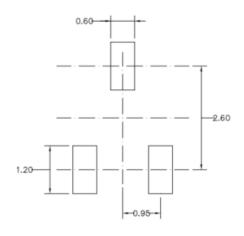

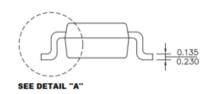

### PACKAGE INFORMATION

TOP VIEW

RECOMMENDED LAND PATTERN

FRONT VIEW

SIDE VIEW

#### **DETAIL A**

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS.

2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

5) DRAWING CONFORMS TO JEDEC MO-193, VARIATION AA.

6) DRAWING IS NOT TO SCALE.

SOT23-3L Package Outline Dimensions

#### NOTE:

- 1. Drawing proposed to be made a JEDEC package outline MO-220 variation.

- 2. Drawing not to scale.

- 3. All linear dimensions are in millimeters.

- 4. Thermal pad shall be soldered on the board.

- 5. Dimensions of exposed pad on bottom of package do not include mold flash.

- 6. Contact PCB board fabrication for minimum solder mask web tolerances between the pins.

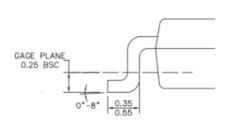

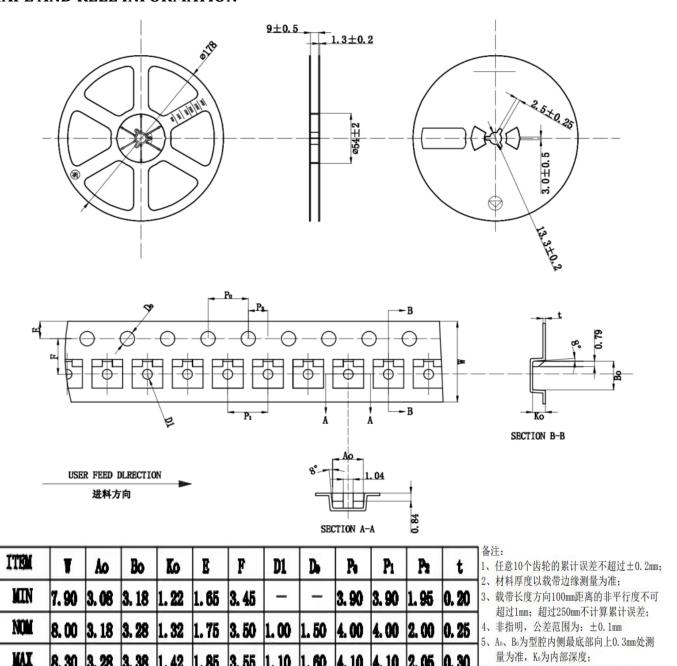

### TAPE AND REEL INFORMATION

| ITEM | W     | Ao    | Во    | Ко    | Е     | F     | D1    | D <sub>0</sub> | Po    | P <sub>1</sub> | P <sub>2</sub> | t     |

|------|-------|-------|-------|-------|-------|-------|-------|----------------|-------|----------------|----------------|-------|

|      | 7. 80 |       |       |       |       |       |       |                |       |                |                | 0. 20 |

| NOM  | 8. 00 | 3. 25 | 3. 30 | 1. 38 | 1. 75 | 3. 50 | 1.00  | 1.50           | 4. 00 | 4. 00          | 2.00           | 0. 25 |

| MAX  | 8. 20 | 3. 35 | 3. 40 | 1. 48 | 1.85  | 3. 55 | 1. 10 | 1.60           | 4. 10 | 4. 10          | 2. 05          | 0.30  |

### 备注:

- 1、任意10个齿轮的累计误差不超过±0.2mm; 2、材料厚度以载带边缘测量为准;

- 3、载带长度方向100mm距离的非平行度不可 超过1mm;超过250mm不计算累计误差;

- 、非指明,公差范围为: ±0.1mm

- 、Ao、Bo为型腔内侧最底部向上0.3mm处测量为准,Ko为内部深度;

- 、型腔外形凡未标明处倒角R为0.2-0.3;

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee the third party Intellectual Property rights are not infringed upon when integrating Silicon Content Technology (SCT) products into any application. SCT will not assume any legal responsibility for any said applications.

### TAPE AND REEL INFORMATION

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee the third party Intellectual Property rights are not infringed upon when integrating Silicon Content Technology (SCT) products into any application. SCT will not assume any legal responsibility for any said applications.

6、型腔外形凡未标明处倒角R为0.2-0.3;